Intel发布全球容量最大FPGA:14nm 443亿晶体管超AMD 64核霄龙

时间:2019-11-08 | 栏目:台式机 | 点击:次

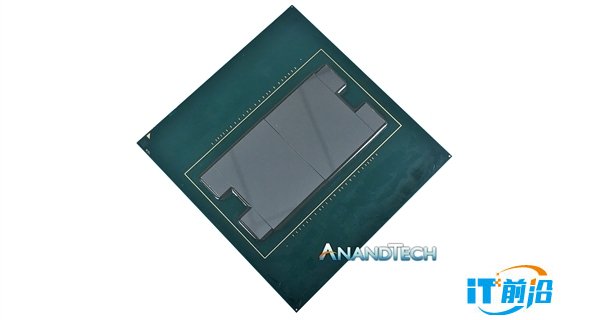

Intel今天宣布推出全球容量最大的FPGA Stratix 10 GX 10M,在70×74毫米的封装面积内拥有多达1020万个逻辑单元,是此前最大Stratix 10 GX 1SG280的大约3.7倍,但是功耗降低了40%。

它采用14nm工艺制造,集成了443亿个晶体管,核心面积约1400平方毫米,也就是每平方毫米3100万个晶体管,同时顺利超越赛灵思8月底发布的Virtex UltraScale+ VU19P FPGA,后者是350亿个晶体管。

Intel如今已经不再公布酷睿、至强处理器的晶体管密度,不过作为参考,AMD 64核心的7nm Zen第二代霄龙处理器有395.4亿个晶体管,16核心的第三代锐龙则是98.9亿个。

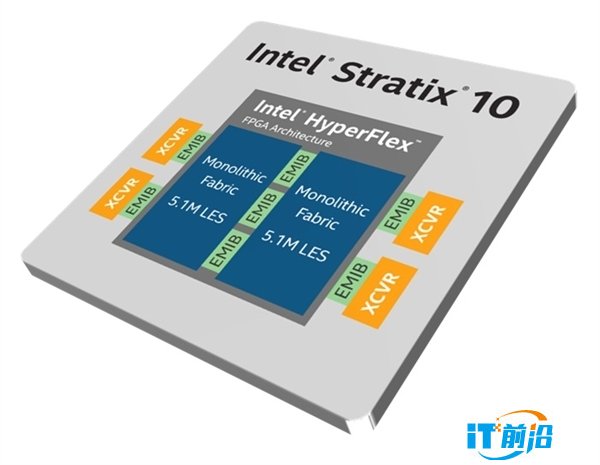

这款元件密度极高的FPGA基于现有的Intel Stratix 10 FPGA架构、Intel EMIB 2.5D(嵌入式多芯片互连桥接)封装技术,融合了两个高密度Stratix 10 GX FPGA,各有510万个逻辑单元,也是第一次使用EMIB技术将两个FPGA在逻辑和电气上实现整合——Intel此前融合了AMD Vega图形核心的Kaby Lake-G处理器就用了EMIB技术。

此外,这款FPGA还有25920个数据接口总线(EMIB),是此前记录的两倍多,每个接口吞吐量2Gbps,内部总带宽6.5TB/s,另有308Mb存储、6912个DSP(18×19排列)、2304个用户I/O针脚、48个收发器(0.84Tb/s带宽)。

Intel指出,使用超大规模FPGA可以在尽可能少的FPGA设备中纳入大型ASIC、ASSP、SoC设计,Stratix 10 FPGA支持仿真和原型设计系统的开发,适用于耗用亿级ASIC门的数字IC设计,并支持Intel Quartus Prime软件套件,采用新款专用IP,明确支持ASIC仿真和原型设计。

FPGA Stratix 10 GX 10M已经投入量产,多家客户也早已拿到样品。